18. Der Analog-Digital Wandler

Der Analog-Digital Wandler hat folgende Eiegnschaften:

Man beachte, dass die Eingänge ADC4 und ADC5 auf 8-bit Genauigkeit limitiert sind, die Eingänge ADC 3 bis 0 und ADC 7 bis 6 haben 10-bit Genauigkeit.

Der ADC enthält einen Sample and Hold Verstärker, der sicherstellt, dass die Eingangsspannung für den Wandler während des Wandlungsvorganges konstant bleibt.

Der ADC hat einen separaten Pin für die Versorgungsspannung (AVCC). AVCC darf nicht mehr als +- 0,3 V von VCC abweichen. Siehe Kapitel ADC Störungsunterdrückung.

Die interne Referenzspannung von nominell 2,56V wird auf dem Chip erzeugt. Die Referenzspannung sollte durch einen externen Kondensator am Pin AREF gestützt werden, um eine Störsicherheit zu erreichen.

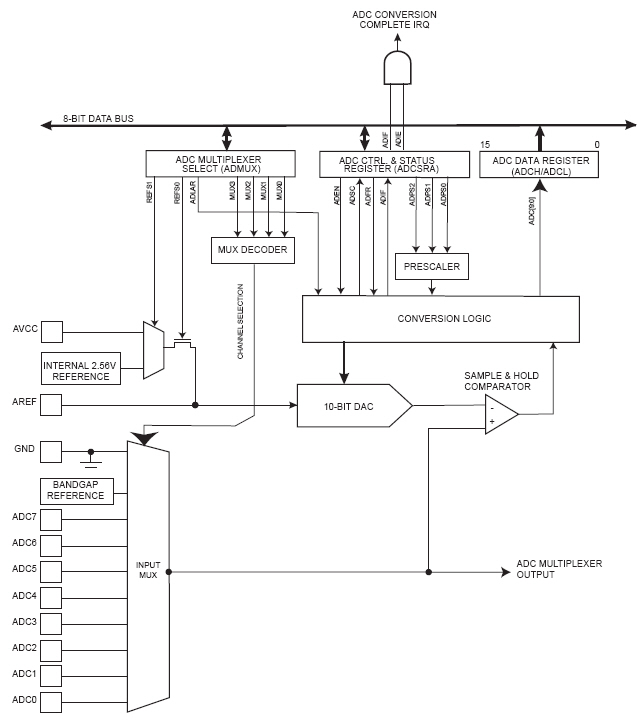

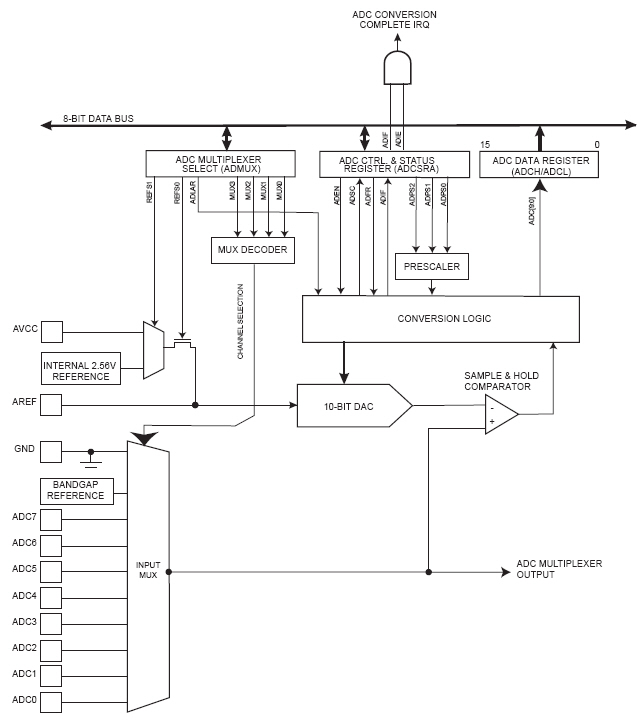

Blockschaltbild des Analog-Digital-Wandlers

Die Referenzspannung für den Analog-Digital-Wandler kann durch die Bits REFS1 und REFS0 im ADMUX-Register ausgewählt werden, die Referenzspannung liegt dann auch am AVCC Pin an. Möglich sind VCC oder die interne Referenzspannung von 2,56V. Die Spannung an AVCC kann durch einen externen Kondensator am AREF-Pin zur besseren Rauschunterdrückung gestützt werden.

Die analogen Eingänge werden mit den Bits MUX2 bis MUX0 im ASMUX-Register ausgewählt. Jeder der Eingänge sowie GND oder die feste Bandgap Referenzspannung können als Einzeleingang für den Analog-Digital-Wandler ausgewählt werden.

Der Analog-Digital-Wandler kann in zwei Arten betrieben werden, der kontinuierlichen oder der einzelnen Wandlung. Bei der Einzelwandlung wird jede Wandlung durch das Programm einzeln gestartet. Bei der kontinuierlichen Wandlung werden die Eingänge ständig ausgewertet und die Daten im ADC Data Register aktualisiert. Das ADFR-Bit im ADCSR-Register wählt zwischen diesen beiden Möglichkeiten aus.

Der Analog-Digital-Wandler wird freigegeben, indem das ADEN-Bit im ADCSR-Register gesetzt wird. Änderungen an der Referenzspannung und den Input Kanälen werden erst wirksam, wenn das ADEN-Bit gesetzt ist. Wenn das ADEN-Bit gelöscht ist, verbraucht der Analog-Digital-Wandler kein Strom. Es ist also sinnvoll, das Bit zu löschen, bevor in den Stromsparmodus umgeschaltet wird.

Der Analog-Digital-Wandler erzeugt ein 10-bit Ergebnis, das in den ADC Data Registern ADCH und ADCL abgelegt wird. Normalerweise wird das Ergebnis rechtsbündig in den beiden Registern abgelegt, optional kann das Ergebnis aber auch linksbündig in ADCH und ADCL geschrieben werden. Die Einstellung erfolgt mit dem ADLAR-Bit im ADMUX-Register.

Wenn das Ergebnis linksbündig geschrieben wird, und keine größere Auflösung als 8 Bit benötigt wird, so kann das komplette (8-Bit) Ergebnis direkt aus ADCH gelesen werden. Andernfalls muss erst ADCL und dann ADCH gelesen werden, um sicherzustellen, dass beide Daten zu dem selben Wandlungsergebnis gehören. Sobald ADCL gelesen wird, kann der Analog-Digital-Wandler keine Zugriffe auf die Datenbytes ausführen. Das bedeutet, dass wenn ADCL gelesen wurde und eine weitere Wandlung abgeschlossen wurde, bevor ADCH ausgelesen ist, werden beide Register nicht mit den neuen Werten beschrieben und das neue Wandlungsergebnis geht verloren. Wenn ADCH gelesen wird, wird der Zugriff auf die Register ADCL und ADCH wieder freigegeben.

Der ADC hat einen eigenen Interrupt, der getriggert werden kann, wenn eine Wandlung abgeschlossen wurde. Wenn der Zugriff des ADC auf die Datenregister zwischen dem Lesen von ADCH und ADCL gesperrt ist, wird der Interrput trotzdem getriggert, auch wenn das Ergebnis verloren geht.

- 10-bit Auflösung (8-bit Genauigkeit bei ADC 4 und ADC5)

- +- 2 LSB absolute Genauigkeit

- 0,5 LSB integrale Nichtlinearität

- optionale Streichung der Offsetspannung

- 65 260 µs Wandlungszeit

- bis zu 15.000 Wandlungen pro Sekunde

- 6 gemultiplexte Einzeleingänge

- 2 weitere gemultiplexte Eingänge im TQFP und MLF Gehäuse

- Auswählbare 2,56 V ADC Referenzspannung

- 0 VCC Eingangsspannung an den Einzeleingängen

- Optionale linksbündiges Aufbereiten für das Auslesen der Wandlungsergebnisse

- Kontinuierliche oder Einzelwandlung

- Interrupt bei Ende der Wandlung

- Sleep-Modus Noise Canceler

Man beachte, dass die Eingänge ADC4 und ADC5 auf 8-bit Genauigkeit limitiert sind, die Eingänge ADC 3 bis 0 und ADC 7 bis 6 haben 10-bit Genauigkeit.

Der ADC enthält einen Sample and Hold Verstärker, der sicherstellt, dass die Eingangsspannung für den Wandler während des Wandlungsvorganges konstant bleibt.

Der ADC hat einen separaten Pin für die Versorgungsspannung (AVCC). AVCC darf nicht mehr als +- 0,3 V von VCC abweichen. Siehe Kapitel ADC Störungsunterdrückung.

Die interne Referenzspannung von nominell 2,56V wird auf dem Chip erzeugt. Die Referenzspannung sollte durch einen externen Kondensator am Pin AREF gestützt werden, um eine Störsicherheit zu erreichen.

Blockschaltbild des Analog-Digital-Wandlers

Blockschaltbild des Analog-Digital Wandlers

Der Analog-Digital-Wandler wandelt eine analoge Eingangsspannung durch succsessive Approximation in einen 10-bit Digitalwert. Der kleinste Wert enstpricht GND, der maximale Wert entspricht der ausgewählten Referenzspannung minus ein LSB.Die Referenzspannung für den Analog-Digital-Wandler kann durch die Bits REFS1 und REFS0 im ADMUX-Register ausgewählt werden, die Referenzspannung liegt dann auch am AVCC Pin an. Möglich sind VCC oder die interne Referenzspannung von 2,56V. Die Spannung an AVCC kann durch einen externen Kondensator am AREF-Pin zur besseren Rauschunterdrückung gestützt werden.

Die analogen Eingänge werden mit den Bits MUX2 bis MUX0 im ASMUX-Register ausgewählt. Jeder der Eingänge sowie GND oder die feste Bandgap Referenzspannung können als Einzeleingang für den Analog-Digital-Wandler ausgewählt werden.

Der Analog-Digital-Wandler kann in zwei Arten betrieben werden, der kontinuierlichen oder der einzelnen Wandlung. Bei der Einzelwandlung wird jede Wandlung durch das Programm einzeln gestartet. Bei der kontinuierlichen Wandlung werden die Eingänge ständig ausgewertet und die Daten im ADC Data Register aktualisiert. Das ADFR-Bit im ADCSR-Register wählt zwischen diesen beiden Möglichkeiten aus.

Der Analog-Digital-Wandler wird freigegeben, indem das ADEN-Bit im ADCSR-Register gesetzt wird. Änderungen an der Referenzspannung und den Input Kanälen werden erst wirksam, wenn das ADEN-Bit gesetzt ist. Wenn das ADEN-Bit gelöscht ist, verbraucht der Analog-Digital-Wandler kein Strom. Es ist also sinnvoll, das Bit zu löschen, bevor in den Stromsparmodus umgeschaltet wird.

Der Analog-Digital-Wandler erzeugt ein 10-bit Ergebnis, das in den ADC Data Registern ADCH und ADCL abgelegt wird. Normalerweise wird das Ergebnis rechtsbündig in den beiden Registern abgelegt, optional kann das Ergebnis aber auch linksbündig in ADCH und ADCL geschrieben werden. Die Einstellung erfolgt mit dem ADLAR-Bit im ADMUX-Register.

Wenn das Ergebnis linksbündig geschrieben wird, und keine größere Auflösung als 8 Bit benötigt wird, so kann das komplette (8-Bit) Ergebnis direkt aus ADCH gelesen werden. Andernfalls muss erst ADCL und dann ADCH gelesen werden, um sicherzustellen, dass beide Daten zu dem selben Wandlungsergebnis gehören. Sobald ADCL gelesen wird, kann der Analog-Digital-Wandler keine Zugriffe auf die Datenbytes ausführen. Das bedeutet, dass wenn ADCL gelesen wurde und eine weitere Wandlung abgeschlossen wurde, bevor ADCH ausgelesen ist, werden beide Register nicht mit den neuen Werten beschrieben und das neue Wandlungsergebnis geht verloren. Wenn ADCH gelesen wird, wird der Zugriff auf die Register ADCL und ADCH wieder freigegeben.

Der ADC hat einen eigenen Interrupt, der getriggert werden kann, wenn eine Wandlung abgeschlossen wurde. Wenn der Zugriff des ADC auf die Datenregister zwischen dem Lesen von ADCH und ADCL gesperrt ist, wird der Interrput trotzdem getriggert, auch wenn das Ergebnis verloren geht.