15.1. Bus Konzept

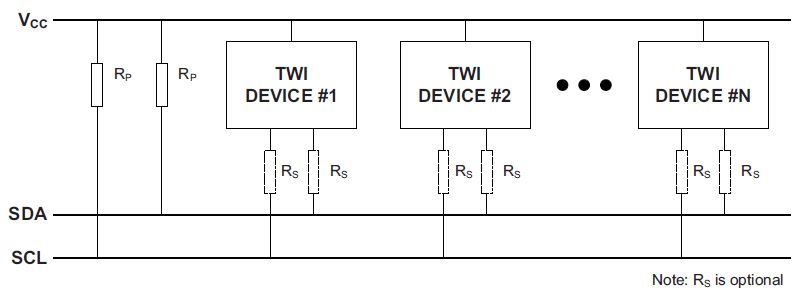

Das TWI ermöglicht eine einfache, bidirektionale Kommunikation über zwei Leitungen, die serielle Taktleitung (SCL) und die serielle Datenleitung (SDA). Die beiden Leitungen sind open collector (wired AND) daher sind zwei pull up Wiederstände die einzigen externen Komponenten, die benötigt werden. Die beiden Widerstände sorgen für H-Pegel auf den Leitungen, der Low-Pegel kommt von den angeschlossenen Bausteinen.

Jeder Baustein, der an den Bus angeschlossen ist, muss eine eigene, einmalige Adresse haben. Ein Ausgleichsmechanismus regelt die Herrschaft über den Bus, wenn mehr als ein Master zur gleichen Zeit die Kontrolle über den Bus haben wollen. Ein Baustein kann sowohl als Master als auch als Slave arbeiten, er kann sogar mehrere Slaves simulieren indem er auf mehrere Adressen reagiert.

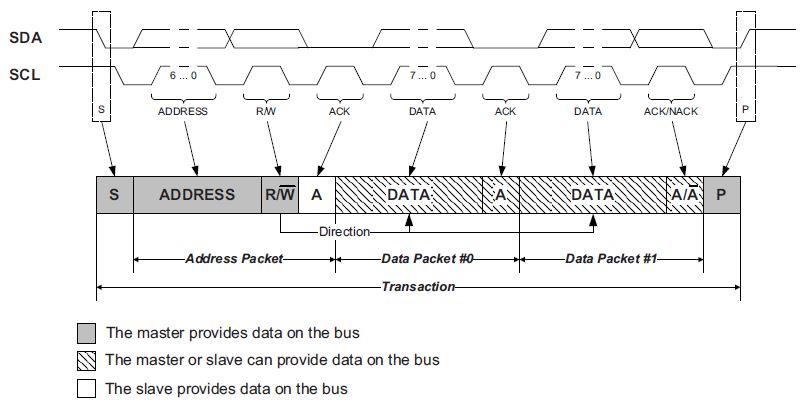

Ein Master beginnt eine Übertragung indem er eine START Bedingung (S) auf dem Bus ausgibt. Danach wird das Adresspaket auf dem Bus ausgegeben. Es enthält die Adresse (ADRESS) und ein Bit, das angibt, ob der Master Daten lesen oder schreiben will (R/W). Nachdem alle Daten (DATA) gesendet wurden, beendet der Master die Übertragung mit einer Stop Bedingung (STOP). Der Empfänger muss jedes empfangene Byte bestätigen (A) oder nicht bestätigen (/A).

Der Master erzeugt den Takt für die Übertragung. Den angeschlossenen Bausteinen ist es jedoch erlaubt, die Low Periode des Taktes zu verlängern und dadurch die Geschwindigkeit zu reduzieren.

TWI Bus Konzept

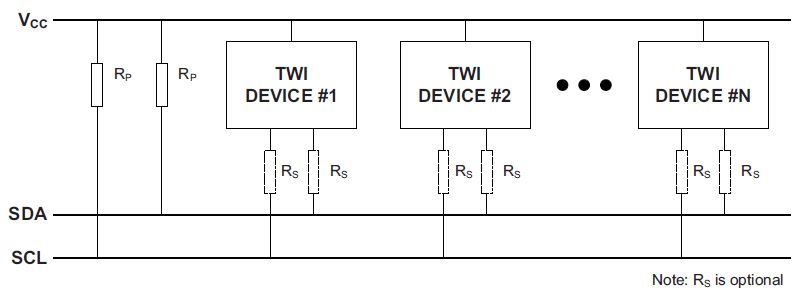

Jeder Baustein, der an den Bus angeschlossen ist, muss eine eigene, einmalige Adresse haben. Ein Ausgleichsmechanismus regelt die Herrschaft über den Bus, wenn mehr als ein Master zur gleichen Zeit die Kontrolle über den Bus haben wollen. Ein Baustein kann sowohl als Master als auch als Slave arbeiten, er kann sogar mehrere Slaves simulieren indem er auf mehrere Adressen reagiert.

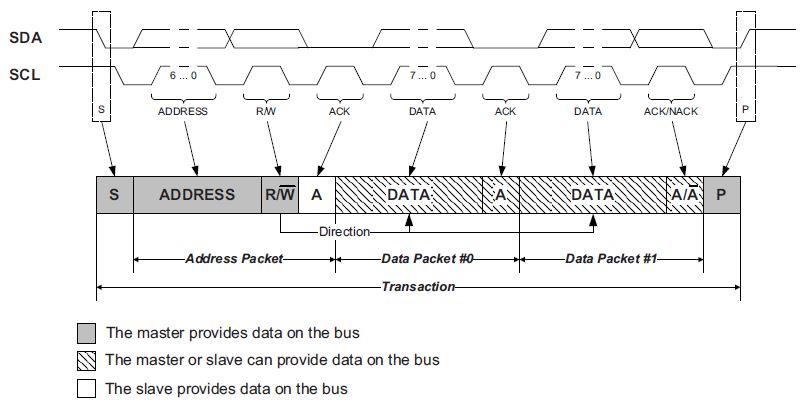

Ein Master beginnt eine Übertragung indem er eine START Bedingung (S) auf dem Bus ausgibt. Danach wird das Adresspaket auf dem Bus ausgegeben. Es enthält die Adresse (ADRESS) und ein Bit, das angibt, ob der Master Daten lesen oder schreiben will (R/W). Nachdem alle Daten (DATA) gesendet wurden, beendet der Master die Übertragung mit einer Stop Bedingung (STOP). Der Empfänger muss jedes empfangene Byte bestätigen (A) oder nicht bestätigen (/A).

TWI Übertragung

Der Master erzeugt den Takt für die Übertragung. Den angeschlossenen Bausteinen ist es jedoch erlaubt, die Low Periode des Taktes zu verlängern und dadurch die Geschwindigkeit zu reduzieren.