2.6. Timing Speicherzugriff und Befehlsauführung

Nachfolgend wird das allgemeine Konzept der Zugriffszeiten bei der Ausführung von Befehlen beschrieben. Die AVR-CPU wird durch den CPU-Takt clkCPU getaktet, der direkt aus der ausgewählten Taktquelle abgeleitet wird, ohne vorher geteilt zu werden.

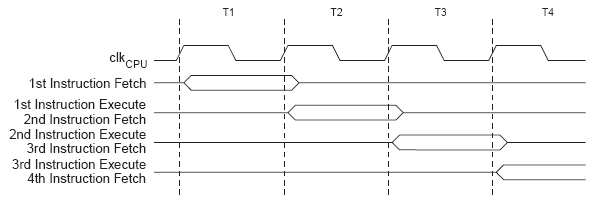

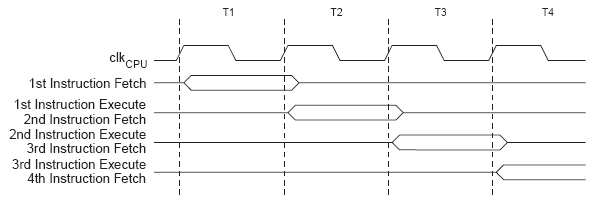

Die nachfolgende Abbildung zeigt das parallele Auslesen und Ausführung von Befehlen, was durch die Harvard-Architektur und den Direktzugriff auf die Register ermöglicht wird. Aufgrund dieses Konzeptes kann ein Durchsatz von 1 MIPS pro MHz erreicht werden.

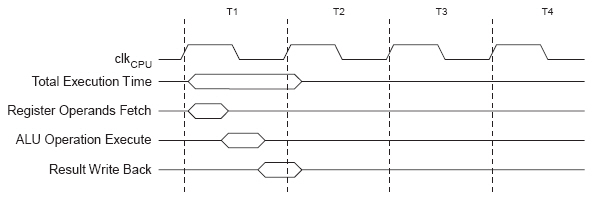

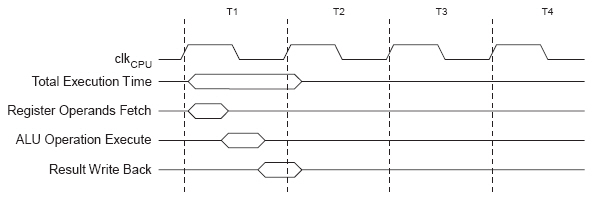

Das Timing bei der Abarbeitung eines Befehles zeigt folgende Abbildung. In einem Takt-Zyklus werden bis zu zwei Register gelesen, die Operation in der ALU ausgeführt und das Ergebnis zurück in ein Register geschrieben.

Die nachfolgende Abbildung zeigt das parallele Auslesen und Ausführung von Befehlen, was durch die Harvard-Architektur und den Direktzugriff auf die Register ermöglicht wird. Aufgrund dieses Konzeptes kann ein Durchsatz von 1 MIPS pro MHz erreicht werden.

Timing Befehl lesen und ausführen

Das Timing bei der Abarbeitung eines Befehles zeigt folgende Abbildung. In einem Takt-Zyklus werden bis zu zwei Register gelesen, die Operation in der ALU ausgeführt und das Ergebnis zurück in ein Register geschrieben.

Timing Befehl ausführen