12.11.4. Phasenkorrekter PWM Modus

Der Phase Correct PWM Modus (WGM13 bis WGM10 = 1, 2, 3, 10 oder 11) bietet eine phasenkorrekte Ausgangswelle mit hoher Auflösung. Der Phase correct PWM Modus basiert, wie der phase an frequenzy correct PWM Modus, auf einer zweifachen Impulsflanke. Der Zähler zählt vom BOTTOM Wert bis zum TOP Wert und wieder zurück vom TOP zum BOTTOM Wert. Im nicht invertierenden Compare Output Mode wird der Output Compare (OC1x) gelöscht, wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen dem TCNT1 und OCR1x auftritt und wird gesetzt wenn beim Runterzählen eine Vergleichsübereinstimmung auftritt. Im invertierenden Output Compare Modus ist es genau umgekehrt. Durch die zweifache Impulsflanke ist die Frequenz im phase correct PWM Modus niedriger als in den PWM Modi, die mit einer einfachen Impulsflanke arbeiten. Wegen der symmetrischen Eigenschaften der PWM Modi mit zweifacher Impulsflanke eigenen sich diese besonders für die Steuerung von Motoren.

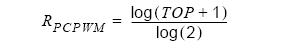

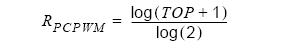

Die PWM Auflösung im Phase Correct PWM Modus kann fest eingestellt werden auf 8-, 9- oder 10-bit, oder durch das ICR1 oder OCR1A festgelegt werden. Die minimale Auflösung beträgt 2 Bit (ICR1 oder OCR1A auf 0003 eingestellt), die maximale Auflösung beträgt 16 Bit (ICR1 oder OCR1A auf MAX eingestellt). Die Auflösung der PWM in Bits kann mit folgender Formel berechnet werden:

Im Phase Correct PWM Modus wird der Zähler so lange inkrementiert, bis der Zähler entweder einen der festen Werte 00FF, 01FF oder 03FF (WGM13 bis WGM10 = 1, 2, oder 3) oder den Wert des ICR1 (WGM13 bis WGM10 = 10) bzw. den Wert des OCR1A (WGM13 bis WGM10 = 11) erreicht. Der Zähler hat dann den TOP Wert erreicht und ändert daraufhin seine Zählrichtung. Der Wert von TCNT1 wird für einen Takt lang gleich dem ausgewählten TOP Wert sein. Das Zeitdiagramm des Phase Correct PWM Modus ist im nachfolgenden Bild zu sehen. Es zeigt den Fall, in dem ICR1 bzw. OCR1A den TOP Wert vorgeben. Der Wert des TCNT1 ist als Histogramm dargestellt, um die zweifache Impulsflanke darzustellen. Auch der invertierende und der nicht invertierende Ausgang sind dargestellt. Die kleinen horizontalen Linien an der TCNT1 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR1x und TCNT1. Das OC1x Interrupt Flag wird gesetzt, wenn eine Vergleichsübereinstimmung auftritt.

Das Timer/Counter Overflow Flag (TOV1) wird jedes Mal gesetzt, wenn der Zähler seinen BOTTOM Wert erreicht. Wenn das OCR1A oder das ICR1 Register den TOP Wert bestimmen werden dementsprechend auch das OCF1A bzw. das ICF1 Flag gesetzt in dem gleichen Timertakt in dem das OCR1x Register mit dem zweifach gebufferten Wert upgedatet wird (bei TOP). Die Interrupt Flags können genutzt werden, um einen Interrupt bei jedem Erreichen des TOP oder BOTTOM Wertes durch den Zähler zu erzeugen.

Wenn der TOP Wert geändert wird, muss das Programm sicherstellen, dass der neue TOP Wert größer oder gleich dem Wert aller Vergleichsregister ist. Ist der neue TOP Wert kleiner, so kann keine Vergleichsübereinstimmung zwischen TCNT1 und OCR1x auftreten. Wenn die festen TOP Werte verwendet werden, werden die ungenutzten Bits mit 0 maskiert wenn eines der OCR1x Register beschrieben wird. Wie in der dritten Periode in dem Zeitdiagramm zu sehen, kann das Verändern des TOP Wertes während des laufenden Betriebes zu einem unsymmetrischen Ausgang führen. Der Grund hierfür liegt in der Zeit, in der das OCR1x Register aktualisiert wird. Weil das OCR1x Register bei Erreichen des TOP Wertes aktualisiert wird, beginnt und endet eine Periode am TOP Wert. Das hat zur Folge, dass die Länge der fallenden Flanke durch den alten TOP Wert bestimmt wird, während sich die Länge der steigenden Flanke aus dem neuen TOP Wert ergibt. Wenn diese beiden Werte unterschiedlich sind unterscheidet sich auch die Länge der beiden Flanken. Der Unterschied in der Länge führt dann zu dem unsymmetrischen Ausgangssignal.

Es wird empfohlen den Phasen und Frequenzkorrekten PWM Modus zu verwenden, wenn der TOP Wert während des laufenden Zählers verändert werden soll. Wenn ein fester TOP Wert verwendet wird, unterscheiden sich diese beiden Modi nicht.

Im Phase correct PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC1x Pins. Durch Setzen der COM1x1 und COM1x0 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt. Ein invertiertes PWM-Signal kann erzeugt werden, indem COM1x1 und COM1x0 auf 3 gesetzt werden. Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC1X = 1). Das PWM Signal wird erzeugt indem das OC1x Register gesetzt (gelöscht) wird, wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht und das OC1x Register wird gelöscht (gesetzt) wird, wenn beim Runterzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht.

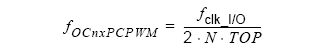

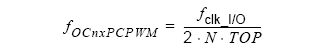

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Extreme Werte der OCR1x Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Phase correct PWM Modus dar. Wenn ein OCR1x Register auf den gleichen Wert wie BOTTOM eingestellt wird, bleibt der Ausgang permanant auf Low-Pegel Das Setzen des OCR1x Registers auf den TOP Wert wird zu einem konstanten High-Pegel am Ausgang führen (beim invertierenden Modus ist es dann genau anders herum).

Wenn das OCR1A verwendet wird, um den TOP Wert festzulegen (WGM13 bis WGM10 = 11) und COM1A1 und COM1A0 auf 1 sind, dann wechselt der OC1A Ausgang mit einem Tastverhältnis von 50%.

Die PWM Auflösung im Phase Correct PWM Modus kann fest eingestellt werden auf 8-, 9- oder 10-bit, oder durch das ICR1 oder OCR1A festgelegt werden. Die minimale Auflösung beträgt 2 Bit (ICR1 oder OCR1A auf 0003 eingestellt), die maximale Auflösung beträgt 16 Bit (ICR1 oder OCR1A auf MAX eingestellt). Die Auflösung der PWM in Bits kann mit folgender Formel berechnet werden:

Auflösung im Phase Correct PWM Modus

Im Phase Correct PWM Modus wird der Zähler so lange inkrementiert, bis der Zähler entweder einen der festen Werte 00FF, 01FF oder 03FF (WGM13 bis WGM10 = 1, 2, oder 3) oder den Wert des ICR1 (WGM13 bis WGM10 = 10) bzw. den Wert des OCR1A (WGM13 bis WGM10 = 11) erreicht. Der Zähler hat dann den TOP Wert erreicht und ändert daraufhin seine Zählrichtung. Der Wert von TCNT1 wird für einen Takt lang gleich dem ausgewählten TOP Wert sein. Das Zeitdiagramm des Phase Correct PWM Modus ist im nachfolgenden Bild zu sehen. Es zeigt den Fall, in dem ICR1 bzw. OCR1A den TOP Wert vorgeben. Der Wert des TCNT1 ist als Histogramm dargestellt, um die zweifache Impulsflanke darzustellen. Auch der invertierende und der nicht invertierende Ausgang sind dargestellt. Die kleinen horizontalen Linien an der TCNT1 Flanke kennzeichnen die Vergleichsübereinstimmung zwischen OCR1x und TCNT1. Das OC1x Interrupt Flag wird gesetzt, wenn eine Vergleichsübereinstimmung auftritt.

Zeitdiagramm Phase Correct PWM Modus

Das Timer/Counter Overflow Flag (TOV1) wird jedes Mal gesetzt, wenn der Zähler seinen BOTTOM Wert erreicht. Wenn das OCR1A oder das ICR1 Register den TOP Wert bestimmen werden dementsprechend auch das OCF1A bzw. das ICF1 Flag gesetzt in dem gleichen Timertakt in dem das OCR1x Register mit dem zweifach gebufferten Wert upgedatet wird (bei TOP). Die Interrupt Flags können genutzt werden, um einen Interrupt bei jedem Erreichen des TOP oder BOTTOM Wertes durch den Zähler zu erzeugen.

Wenn der TOP Wert geändert wird, muss das Programm sicherstellen, dass der neue TOP Wert größer oder gleich dem Wert aller Vergleichsregister ist. Ist der neue TOP Wert kleiner, so kann keine Vergleichsübereinstimmung zwischen TCNT1 und OCR1x auftreten. Wenn die festen TOP Werte verwendet werden, werden die ungenutzten Bits mit 0 maskiert wenn eines der OCR1x Register beschrieben wird. Wie in der dritten Periode in dem Zeitdiagramm zu sehen, kann das Verändern des TOP Wertes während des laufenden Betriebes zu einem unsymmetrischen Ausgang führen. Der Grund hierfür liegt in der Zeit, in der das OCR1x Register aktualisiert wird. Weil das OCR1x Register bei Erreichen des TOP Wertes aktualisiert wird, beginnt und endet eine Periode am TOP Wert. Das hat zur Folge, dass die Länge der fallenden Flanke durch den alten TOP Wert bestimmt wird, während sich die Länge der steigenden Flanke aus dem neuen TOP Wert ergibt. Wenn diese beiden Werte unterschiedlich sind unterscheidet sich auch die Länge der beiden Flanken. Der Unterschied in der Länge führt dann zu dem unsymmetrischen Ausgangssignal.

Es wird empfohlen den Phasen und Frequenzkorrekten PWM Modus zu verwenden, wenn der TOP Wert während des laufenden Zählers verändert werden soll. Wenn ein fester TOP Wert verwendet wird, unterscheiden sich diese beiden Modi nicht.

Im Phase correct PWM Modus erlauben die Vergleichseinheiten das Erzeugen von PWM Signalen an den OC1x Pins. Durch Setzen der COM1x1 und COM1x0 Bits auf 2 wird ein nicht invertiertes PWM-Signal erzeugt. Ein invertiertes PWM-Signal kann erzeugt werden, indem COM1x1 und COM1x0 auf 3 gesetzt werden. Um das PWM Signal am Port Pin sichtbar zu machen muss dieser als Ausgang konfiguriert werden (DDR_OC1X = 1). Das PWM Signal wird erzeugt indem das OC1x Register gesetzt (gelöscht) wird, wenn beim Hochzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht und das OC1x Register wird gelöscht (gesetzt) wird, wenn beim Runterzählen eine Vergleichsübereinstimmung zwischen OCR1x und TCNT1 besteht.

Die Frequenz des Ausgangssignals kann mit folgender Formel berechnet werden:

Frequenz des Ausgangssignals

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Extreme Werte der OCR1x Register stellen spezielle Fälle bei der Erzeugung des PWM Signals im Phase correct PWM Modus dar. Wenn ein OCR1x Register auf den gleichen Wert wie BOTTOM eingestellt wird, bleibt der Ausgang permanant auf Low-Pegel Das Setzen des OCR1x Registers auf den TOP Wert wird zu einem konstanten High-Pegel am Ausgang führen (beim invertierenden Modus ist es dann genau anders herum).

Wenn das OCR1A verwendet wird, um den TOP Wert festzulegen (WGM13 bis WGM10 = 11) und COM1A1 und COM1A0 auf 1 sind, dann wechselt der OC1A Ausgang mit einem Tastverhältnis von 50%.