12.11.2. Clear Timer on Compare Match (CTC) Modus

Im Clear Timer on Compare Modus (CTC) (WGM13 bis WGM10 = 4 oder 12) werden die Register OCR1A oder ICR1 dazu verwendet, die Auflösung des Timers zu manipulieren. Im CTC Modus wird der Zähler gelöscht, wenn der Wert des Zählers (TNCT1) entweder mit dem des OCR1A Registers (WGM13 bis WGM10 = 4) oder dem des ICR1 Registers (WGM13 bis WGM10 = 12) übereinstimmt. Die beiden Register OCR1A und ICR1 bestimmen also den Maximalwert des Zählers und somit seine Auflösung. Dieser Modus erlaubt eine größere Kontrolle der Compare Match Ausgangsfrequenz. Er vereinfacht auch das Zählen externer Ereignisse.

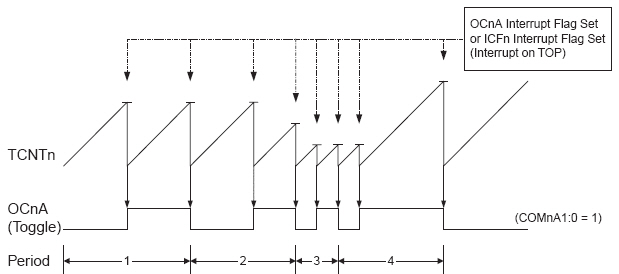

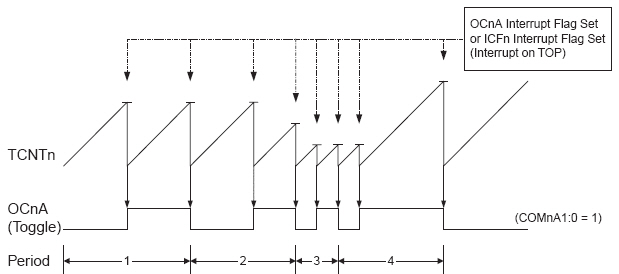

Das Zeitdiagramm des CTC Modus ist nachfolgend abgebildet. Der Wert des Zählers (TCNT1) wächst so lange bis eine Vergleichsgleichheit mit dem OCR1A oder ICR1 auftritt, dann wird der Zähler (TCNT1) gelöscht.

Durch die Flags OCF1A oder ICF1 kann ein Interrupt generiert werden, zu jedem Zeitpunkt, wenn der Wert des Zählers den TOP Wert erreicht, der durch das OCR1A oder ICR1 Register vorgegeben ist. Wenn der Interrupt freigegeben ist, kann die Interruptroutine dazu verwendet werden, um den TOP Wert zu verändern. Das Einstellen des TOP Wertes in die Nähe des BOTTOM Wertes muss mit Vorsicht geschehen, wenn der Zähler ohne oder mit einem geringen Vorteiler betrieben wird, da der CTC Modus keine Zweifachbuffer Eigenschaft hat. Wenn ein neuer Wert in das OCR1A oder ICR1 Register geschrieben wird, der kleiner als der aktuelle Wert des TCNT1 ist, so wird zunächst keine Vergleichsübereinstimmung erkannt. Der Zähler wird dann zunächst bis zu seinem maximalen Wert (FFFF) laufen und von 0000 erneut starten, erst dann kann eine Vergleichsübereinstimmung erkannt werden. In vielen Fällen ist dieses Verhalten nicht wünschenswert. Eine Alternative ist dann die Verwendung des Fast PWM Modus, in dem OCR1A den TOP Wert bildet, der zweifach gebuffert ist.

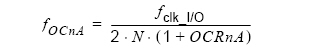

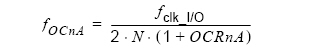

Beim Generieren einer Ausgangsfrequenz im CTC Modus kann der OC1A Ausgang so eingestellt werden, dass er seinen Zustand bei jeder Vergleichsübereinstimmung wechselt, indem die COM1A1 und COM1A0 Bits auf 1 gesetzt werden. Der OC1A Wert wird nicht am Port Pin erscheinen, wenn die Datenrichtung nicht auf Ausgang (DDR_OC1A = 1) eingestellt ist. Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC1A = fclk_I/O/2 haben, wenn OCR1A auf 0000 gesetzt wird. Allgemein wird die Ausgangsfrequenz mit folgender Gleichung bestimmt:

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Im normalen Modus wird das TOV1 Flag in dem selben Taktzyklus gesetzt, in dem der Zähler von seinem MAX Wert auf 0000 wechselt.

Das Zeitdiagramm des CTC Modus ist nachfolgend abgebildet. Der Wert des Zählers (TCNT1) wächst so lange bis eine Vergleichsgleichheit mit dem OCR1A oder ICR1 auftritt, dann wird der Zähler (TCNT1) gelöscht.

Zeitdiagramm des CTC Modus

Durch die Flags OCF1A oder ICF1 kann ein Interrupt generiert werden, zu jedem Zeitpunkt, wenn der Wert des Zählers den TOP Wert erreicht, der durch das OCR1A oder ICR1 Register vorgegeben ist. Wenn der Interrupt freigegeben ist, kann die Interruptroutine dazu verwendet werden, um den TOP Wert zu verändern. Das Einstellen des TOP Wertes in die Nähe des BOTTOM Wertes muss mit Vorsicht geschehen, wenn der Zähler ohne oder mit einem geringen Vorteiler betrieben wird, da der CTC Modus keine Zweifachbuffer Eigenschaft hat. Wenn ein neuer Wert in das OCR1A oder ICR1 Register geschrieben wird, der kleiner als der aktuelle Wert des TCNT1 ist, so wird zunächst keine Vergleichsübereinstimmung erkannt. Der Zähler wird dann zunächst bis zu seinem maximalen Wert (FFFF) laufen und von 0000 erneut starten, erst dann kann eine Vergleichsübereinstimmung erkannt werden. In vielen Fällen ist dieses Verhalten nicht wünschenswert. Eine Alternative ist dann die Verwendung des Fast PWM Modus, in dem OCR1A den TOP Wert bildet, der zweifach gebuffert ist.

Beim Generieren einer Ausgangsfrequenz im CTC Modus kann der OC1A Ausgang so eingestellt werden, dass er seinen Zustand bei jeder Vergleichsübereinstimmung wechselt, indem die COM1A1 und COM1A0 Bits auf 1 gesetzt werden. Der OC1A Wert wird nicht am Port Pin erscheinen, wenn die Datenrichtung nicht auf Ausgang (DDR_OC1A = 1) eingestellt ist. Die erzeugte Ausgangswelle kann eine maximale Frequenz von fOC1A = fclk_I/O/2 haben, wenn OCR1A auf 0000 gesetzt wird. Allgemein wird die Ausgangsfrequenz mit folgender Gleichung bestimmt:

Gleichung für Ausgangsfrequenz

Die Variable N steht für den Faktor des Vorteilers (1, 8, 64, 256 oder 1024).

Im normalen Modus wird das TOV1 Flag in dem selben Taktzyklus gesetzt, in dem der Zähler von seinem MAX Wert auf 0000 wechselt.