11.3. Externe Taktquelle

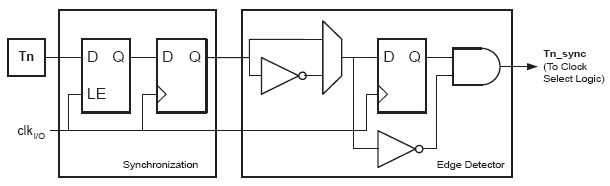

Eine externe Taktquelle an den Pins T0 und T1 kann verwendet werden, um als Takt clkT0 und clkT1 für die Timer/Counter zu dienen. Die T0/T1 Pins werden einmal während jedes Systemtaktes durch die Synchronisationslogik abgetastet. Das synchronisierte (abgetastete) Signal wird dann an einen Flankenerkenner weitergeleitet. Das nachfolgende Abbild zeigt das Blockdiagramm der Synchronisation und Flankenerkennung. Die Register werden durch die positive Flanke des internen Systemtaktes clkI/O. Das Latch ist während der positiven Periode des internen Systemtaktes transparent.

Der Flankenerkenner generiert einen Puls der clkT1/clkT0 Takte bei jeder positiven (CSn2 bis CSn0 = 111) bzw. negativen (CSn2 bis CSn0 = 110)Flanke, die er erkennt.

Die Synchronisation und die Flankenerkennung erzeugen eine Verzögerung von 2,5 bis 3,5 Systemtakten zwischen dem Auftreten der Flanke am T9/T1 Pin und dem Inkrementieren des Zählers.

Das Freigeben und Sperren des Takteinganges muss ausgeführt werden, solange T1/T0 für mindestens einen Systematakt stabil sind, da andernfalls ein ungewollter Taktimpuls für den Timer/Counter erzeugt werden kann.

Jede Hälfte des externen Taktsignals muss länger sein, als ein Zyklus des internen Taktsignals um ein korrektes Abtasten des Signals sicherzustellen. Die Frequenz des externen Signals darf maximal halb so groß sein wie die Frequenz des internen Systemtaktes, wenn das Puls-Pausenverhältnis 1:1 beträgt (Abtasttheorem). Da es immer Toleranzen beim Systemtakt selbst wie auch bei dem externen Takt geben kann, sollte die Frequenz des externen Signals kleiner als fclk_I/O/2,5 sein. Ein externes Signal kann nicht vorgeteilt werden.

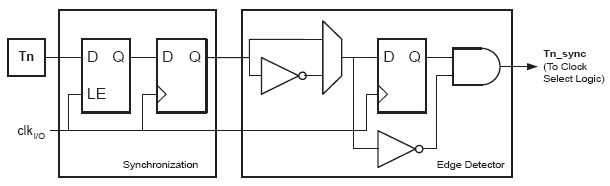

Der Flankenerkenner generiert einen Puls der clkT1/clkT0 Takte bei jeder positiven (CSn2 bis CSn0 = 111) bzw. negativen (CSn2 bis CSn0 = 110)Flanke, die er erkennt.

Pin Sampling T1/T0

Die Synchronisation und die Flankenerkennung erzeugen eine Verzögerung von 2,5 bis 3,5 Systemtakten zwischen dem Auftreten der Flanke am T9/T1 Pin und dem Inkrementieren des Zählers.

Das Freigeben und Sperren des Takteinganges muss ausgeführt werden, solange T1/T0 für mindestens einen Systematakt stabil sind, da andernfalls ein ungewollter Taktimpuls für den Timer/Counter erzeugt werden kann.

Jede Hälfte des externen Taktsignals muss länger sein, als ein Zyklus des internen Taktsignals um ein korrektes Abtasten des Signals sicherzustellen. Die Frequenz des externen Signals darf maximal halb so groß sein wie die Frequenz des internen Systemtaktes, wenn das Puls-Pausenverhältnis 1:1 beträgt (Abtasttheorem). Da es immer Toleranzen beim Systemtakt selbst wie auch bei dem externen Takt geben kann, sollte die Frequenz des externen Signals kleiner als fclk_I/O/2,5 sein. Ein externes Signal kann nicht vorgeteilt werden.

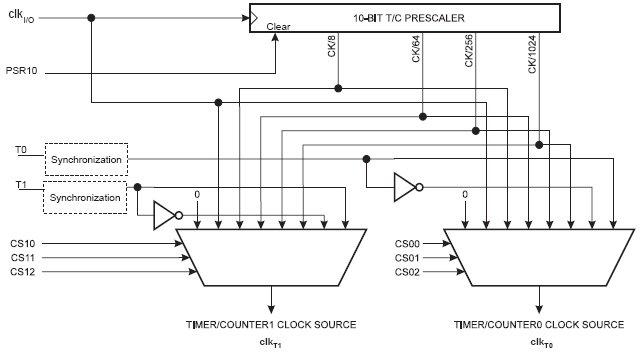

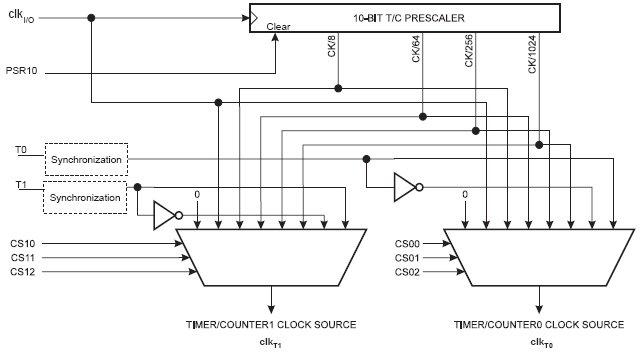

Vorteiler Timer0/Timer1