8.1.2. Lesen der Pinzustände

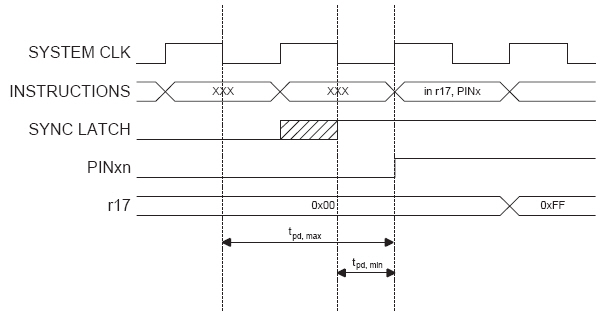

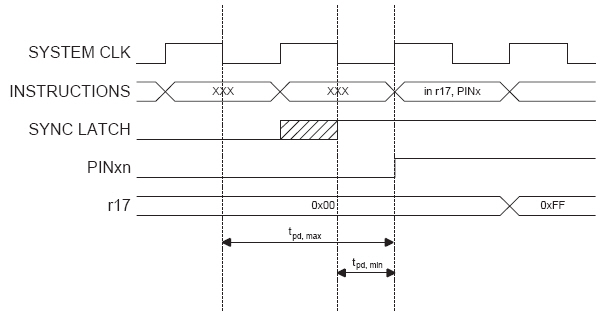

Unabhängig davon, ob ein Pin als Ausgang oder als Eingang konfiguriert ist, kann der Port Pin über das PINxn Register Bit eingelesen werden. Wie aus der internen Schaltung eines Port Pins ersichtlich wird, bilden das PINxn Register Bit und das vorgeschaltete Latch einen Synchronisierer. Dieser ist erforderlich um unstabile Zustände zu vermeiden, wenn der physikalische Port seinen Wert in der Nähe einer Flanke des internen Taktes ändert. Allerdings wird dadurch auch eine Verzögerung eingeleitet. Das nachfolgende Bild zeigt das Zeitdiagramm beim Lesen eines extern angelegten Pinzustandes. Die maximal und minimal auftretende Verzögerung werden als tpd,max und tpd,min bezeichnet.

Man beachte, dass die Taktperiode unmittelbar nach der fallenden Flanke des Systemtaktes beginnt. Das Latch ist geschlossen, solange der Takt auf Low ist, und wird transparent, wenn der Takt auf High ist, was durch die schraffiert Fläche angedeutet ist. Der Eingangszustand des Pins wird dann mit der fallenden Flanke des Systemtaktes in das Latch gespeichert und mit der darauffolgenden positiven Flanke in das PINxn Register übernommen. Dadurch wird die Übernahme eines neuen Zustandes an einem Port Pin mit einer Verzögerung zwischen ½ und 1 ½ Takten durchgeführt.

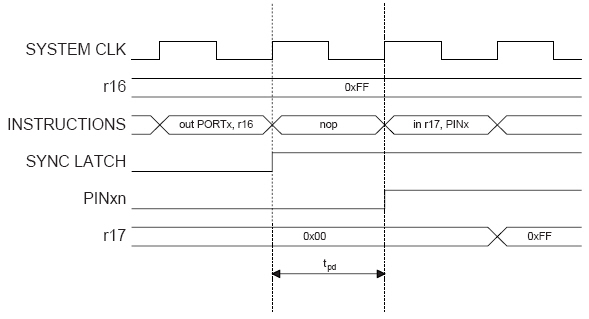

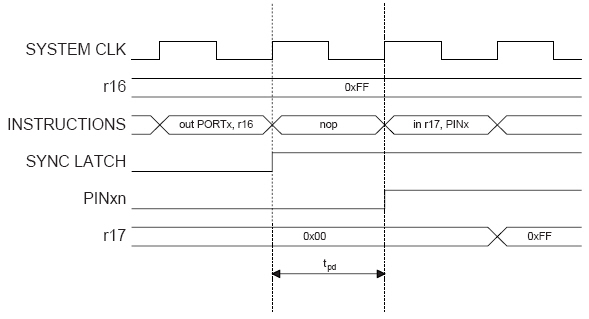

Wenn der durch die Software eingestellte Wert des Pins ausgelesen werden soll, muss ein NOP-Befehl wie nachfolgend dargestellt eingefügt werden, bevor der Wert wieder ausgelesen werden kann. Der OUT-Befehl setzt das SYNC LATCH Signal mit der positiven Flanke des Taktes, erst bei der darauf folgenden positiven Flanke wird der Wert dann in das PINxn Register übernommen und kann wieder ausgelesen werden. In diesem Fall beträgt die Verzögerung tpd durch den Synchronisierer also 1 Taktzyklus.

Das nachfolgende Beispiel zeigt, wie die Pins 0 und 1 von Port B auf High sowie die Pins 2 und 3 auf Low gesetzt werden. Gleichzeitig werden die Pins 4 bis 7 als Eingänge konfiguriert und die Pins 6 und 7 mit den internen pull-up Widerständen versehen. Die Werte der Pins werden zurückgelesen, nachdem wie zuvor besprochen ein NOP-Befehl ausgeführt wurde.

Lesen externer Pinzustand

Man beachte, dass die Taktperiode unmittelbar nach der fallenden Flanke des Systemtaktes beginnt. Das Latch ist geschlossen, solange der Takt auf Low ist, und wird transparent, wenn der Takt auf High ist, was durch die schraffiert Fläche angedeutet ist. Der Eingangszustand des Pins wird dann mit der fallenden Flanke des Systemtaktes in das Latch gespeichert und mit der darauffolgenden positiven Flanke in das PINxn Register übernommen. Dadurch wird die Übernahme eines neuen Zustandes an einem Port Pin mit einer Verzögerung zwischen ½ und 1 ½ Takten durchgeführt.

Wenn der durch die Software eingestellte Wert des Pins ausgelesen werden soll, muss ein NOP-Befehl wie nachfolgend dargestellt eingefügt werden, bevor der Wert wieder ausgelesen werden kann. Der OUT-Befehl setzt das SYNC LATCH Signal mit der positiven Flanke des Taktes, erst bei der darauf folgenden positiven Flanke wird der Wert dann in das PINxn Register übernommen und kann wieder ausgelesen werden. In diesem Fall beträgt die Verzögerung tpd durch den Synchronisierer also 1 Taktzyklus.

Lesen interner Pinzustand

Das nachfolgende Beispiel zeigt, wie die Pins 0 und 1 von Port B auf High sowie die Pins 2 und 3 auf Low gesetzt werden. Gleichzeitig werden die Pins 4 bis 7 als Eingänge konfiguriert und die Pins 6 und 7 mit den internen pull-up Widerständen versehen. Die Werte der Pins werden zurückgelesen, nachdem wie zuvor besprochen ein NOP-Befehl ausgeführt wurde.

Beispiel für Pinkonfiguration

Hinweis: Die temporären Register R16 und R17 werden verwendet, um die Zeit zu minimieren, in der die pull-up Widerstände an den Pins 0, 1, 6 und 7 gesetzt werden und während die Richtungsbits korrekt eingestellt sind und die Bits 2 und 2 als Low und die Bits 0 und 1 als High getriebene Ausgänge eingestellt werden.