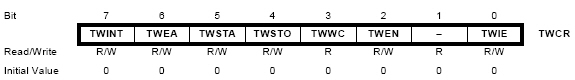

16.6.2. TWCR TWI Control Register

Das TWCR wird verwendet, um die Arbeit des TWI zu kontrollieren. Es wird verwendet, um den TWI freizugeben, um einen Masterzugriff durch Aussenden einer Start-Bedingung zu beginnen, um die Emfangsbestätigung zu erzeugen, um eine Stopp-Bedingung zu erzeugen und um den Takt anzuhalten, während die Daten, die auf den Bus geschrieben werden sollen in das TWDR Register geschrieben werden. Es zeigt ebenfalls eine Schreibkollision wenn versucht wird, Daten in das TWDR zu schreiben, während dieses Register nicht ansprechbar ist.

2. Ein Rundruf wurde empfangen während das TWGCE Bit im TWAR gesetzt war

3. Ein Datenbyte wurde im Master- oder Slave-Modus empfangen.

Durch Setzen dieses Bits auf Null kann der Baustein vorübergehend virtuell vom Bus getrennt werden. Die Adresserkennung kann dann wieder freigegeben werden, indem das Bit wieder auf 1 gesetzt wird.

TWCR Register des ATmega8

Bit 7 TWINT: TWI Interrupt Flag

Diese Bits wird durch die Hardware gesetzt, wenn das TWI seinen laufenden Job beendet hat und auf eine Antwort der Applikationssoftware wartet. Wenn das I-Bit im SREG und das TWIE-Bit im TWCR gesetzt sind, springt die MCU zu dem TWI Interrupt Vektor. Während das TWINT Flag gesetzt ist, wird der SCL Takt auf Low gehalten. Das TWINT Flag wird nicht automatisch durch die Hardware gelöscht, wenn der Interrupt ausgeführt wird. Das Flag muss vielmehr durch die Software gelöscht werden, indem es mit einer logischen 1 beschrieben wird. Das Löschen des Flags startet die Arbeit des TWI wieder, daher müssen alle Zugriffe auf das TWI Address Register (TWAR), das TWI Status Register (TWSR) und das TWI Data Register (TWDR) vorher abgeschlossen sein.Bit 6 TWEA: TWI Enable Acknowledge Bit

Diese Bits kontrolliert das Erzeugen des Empfangsbestätigungs Pulses. Wenn das TWEA Bit mit einer 1 beschrieben ist, so wird ein ACK Puls erzeugt, wenn eine der folgenden Bedingungen zutrifft. 1. Die Slaveadresse des Bausteins wurde empfangen2. Ein Rundruf wurde empfangen während das TWGCE Bit im TWAR gesetzt war

3. Ein Datenbyte wurde im Master- oder Slave-Modus empfangen.

Durch Setzen dieses Bits auf Null kann der Baustein vorübergehend virtuell vom Bus getrennt werden. Die Adresserkennung kann dann wieder freigegeben werden, indem das Bit wieder auf 1 gesetzt wird.