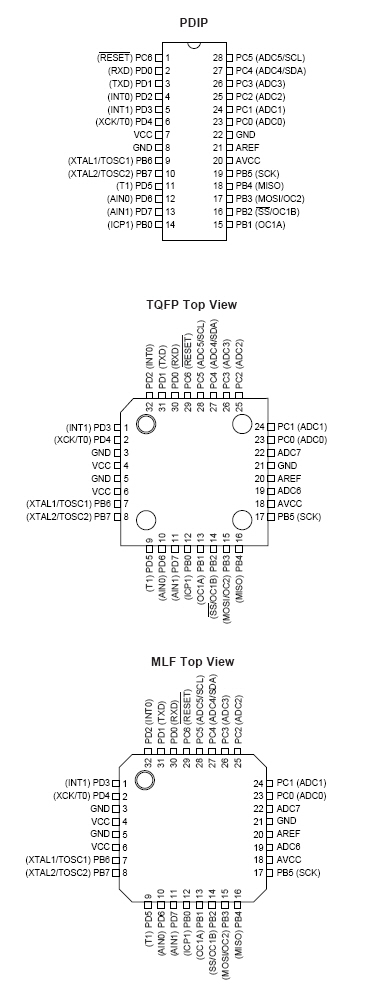

1.2. Anschlussbelegung / Pins des ATmega8

Pinbelegung des ATmega8

| VCC | Digitale positive Versorgungsspannung (2,7 5,5 Volt) |

| GND | Masse Anschluß |

| Port B (PB7..PB0) XTAL1, XTAL2, TOSC1, TOSC2 | Port B ist ein 8 Bit breiter bidirektionaler I/O-Port mit internen pull-up Widerständen, die für jeden Portpin einzeln ein- und ausgeschaltet werden können. Die Ausgangspuffer von Port B sind symmetrisch und liefern sowohl positive als auch negative Ströme. Wenn die Portpins als Eingang geschaltet sind, ziehen sie einen Strom über die internen pull-up Widerstände, wenn diese eingeschaltet sind. Nach einem Reset oder wenn der Takt gesperrt ist, werden die Portpins in Tristate geschaltet. Abhängig von der Programmierung der Fuse-Bits kann der Pin PB6 (XTAL1) als Eingang für den invertierenden Oszillatorverstärker oder als Eingang für den internen Taktgenerator genutzt werden. PB7 (XTAL2) bildet, abhängig von der Programmierung der Fuse-Bits, den Ausgang des invertierenden Oszillatorverstärkers. Wenn der interne RC-Oszillator als Taktquelle verwendet wird, können die Pins PB6 und PB7 auch als TOSC1..2 Eingänge für den asynchronen Timer/Counter2 verwendet werden. Eine genauere Beschreibung der alternativen Funktionen von Port B findet sich unter der Beschreibung der Ports und der Beschreibung der Taktversorgung. |

| Port C (PC0..PC5) | Port C ist ein 7 Bit breiter bidirektionaler I/O-Port mit internen pull-up Widerständen, die für jeden Portpin einzeln ein- und ausgeschaltet werden können. Die Ausgangspuffer von Port C sind symmetrisch und liefern sowohl positive als auch negative Ströme. Wenn die Portpins als Eingang geschaltet sind, ziehen sie einen Strom über die internen pull-up Widerstände, wenn diese eingeschaltet sind. Nach einem Reset oder wenn der Takt gesperrt ist, werden die Portpins in Tristate geschaltet. |

| PC6 / Reset | Wenn die RSTDISBL-Fuse programmiert ist, wird Pin PC6 als normaler I/O-Pin verwendet. Allerdings sind die elektrischen Eigenschaften von Pin PC6 in diesem Falle anders als bei den übrigen Pins von Port C. Wenn die RSTDISBL-Fuse nicht programmiert ist, dann ist der PC6-Pin der Reset-Eingang des Bausteins. Ein Low-Pegel an diesem Pin wird dann, wenn dieser länger als die minimale Pulslänge anliegt, einen Reset auslösen, auch wenn der Takt nicht läuft. Siehe Teil Systemkontrolle und Reset |

| Port D (PD0..PD5) | Port D ist ein 8 Bit breiter bidirektionaler I/O-Port mit internen pull-up Widerständen, die für jeden Portpin einzeln ein- und ausgeschaltet werden können. Die Ausgangspuffer von Port D sind symmetrisch und liefern sowohl positive als auch negative Ströme. Wenn die Portpins als Eingang geschaltet sind, ziehen sie einen Strom über die internen pull-up Widerstände, wenn diese eingeschaltet sind. Nach einem Reset oder wenn der Takt gesperrt ist, werden die Portpins in Tristate geschaltet. |

| AVCC | Ist der Anschluss für die (analoge) Versorgungsspannung des Analog-Digitalwandlers (PortC (3..0) und ADC(7..6)). Wenn dieser nicht verwendet wird, muss der Anschluss an VCC angeschlossen werden. Wird der Analog-Digitalwandler in der Schaltung verwendet, so kann der Anschluss über einen Tiefpassfilter mit VCC verbunden werden. Die Portpins PC4 und PC5 verwenden aber auf jeden Fall digitale Versorgungsspannung VCC. |

| AREF | Hier kann eine Referenzspannung für den Analog-Digitalwandler angelegt werden, wenn nicht die interne Referenzspannung des ATmega8 verwendet werden soll. |

| ADC 7..6 (nur bei TQFP und MLF Gehäuse) | In den Bausteinen im TQFP und MLF Gehäuse stehen zwei weitere Anschlüsse zur Verfügung. ADC7 und ADC6 arbeiten als weitere Eingänge für den Analog-Digitalwandler. Sie arbeiten ebenfalls mit der analogen Versorgungsspannung und mit 10 Bit Auflösung. |