3.2. Datenspeicher des Xmega384

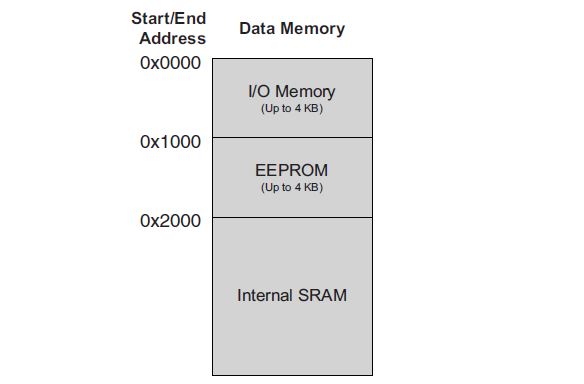

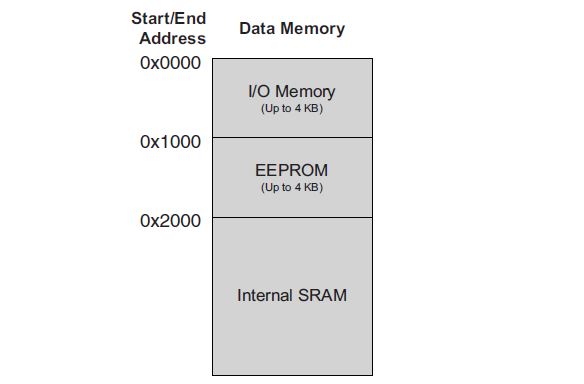

Der Datenspeicher besteht aus I/O-Speicher, SRAM und EEPROM.

Datenspeicher im Xmega384

I/O Speicher (4k)

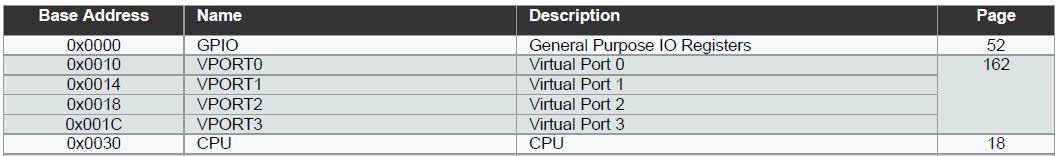

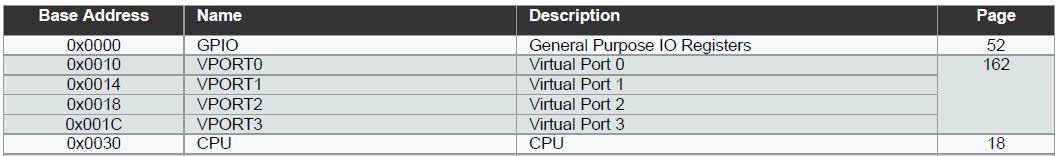

Beginnt immer an Adresse 0x0000 (hex) und geht bis 0x0FFF. Er enthält die Status- und Konfigurationsregister der Module und Peripherie des Controllers. Auf alle Speicherstellen kann mit LD/LDS/LDD zum Lesen und ST/STS/STD zum Schreiben zugegriffen werden. Mit den IN und OUT Befehlen kann auf die Adressen 0x00 bis 0x3F zugegriffen werden. Im Adressbereich 0x00 bis 0x1F können auch einzelne Bits geprüft und geändert werden.

Bitadressierbare Register