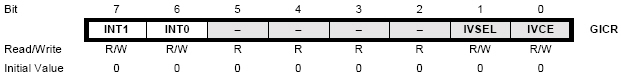

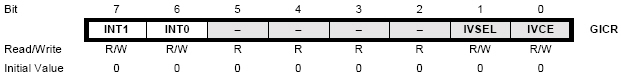

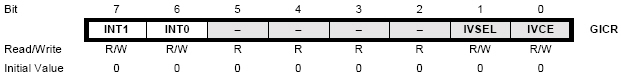

GICR Register des ATmega8

Bit 7 INT1: Externer Interrupt 1 Freigabe

Wenn das INT1-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist, dann ist der externe Interrupt1 freigegeben. Mit den Interrupt Sense Control1 Bits 1 und 0 (ISC11 und ISC10) im General Control Register (MCUCR) wird festgelegt, bei welcher Bedingung ein externer Interrupt erkannt wird. Möglich sind: Steigende oder fallende Flanke, bei Pin-Wechsel oder bei Low-Pegel am INT1-Pin. Die Bedingungen am Pin INT1 werden auch dann eine Interruptanforderung veranlassen, wenn INT1 als Output konfiguriert ist. Die Interruptadresse für den Interrupt ist der Interrupt Vektor INT1.

Bit 6 INT0: Externer Interrupt 0 Freigabe

Wenn das INT0-Bit gesetzt ist und das I-Bit in Status-Register (SREG) ebenfalls gesetzt ist, dann ist der externe Interrupt0 freigegeben. Mit den Interrupt Sense Control0 Bits 1 und 0 (ISC01 und ISC00) im General Control Register (MCUCR) wird festgelegt, bei welcher Bedingung ein externer Interrupt erkannt wird. Möglich sind: Steigende oder fallende Flanke, bei Pin-Wechsel oder bei Low-Pegel am INT0-Pin. Die Bedingungen am Pin INT0 werden auch dann eine Interruptanforderung veranlassen, wenn INT0 als Output konfiguriert ist. Die Interruptadresse für den Interrupt ist der Interrupt Vektor INT0.

Bit 5 bis 2 Res : Reservierte Bits

Diese Bits sind reserviert und werden immer als 0 gelesen.

Bit 1 und 0 werden an anderer Stelle beschrieben